WOLFRAM SYSTEM MODELER

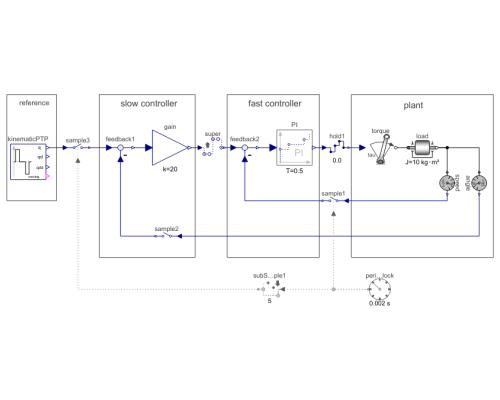

SubClockedDrive with clocked cascade controller where clocks are defined with sub-sampling and partitions with super-sampling |

|

Diagram

Wolfram Language

SystemModel["Modelica.Clocked.Examples.CascadeControlledDrive.SubClocked"]

Information

This information is part of the Modelica Standard Library maintained by the Modelica Association.

Cascade control drive with discrete-time controller where one periodic clock is defined, the second periodic clock is derived by sub-sampling of the first clock, and both clocks are associated to the corresponding controller partitions. The super-sampling factor of block "super" is derived by clock inference.

Components (16)

| load |

Type: Inertia Description: 1D-rotational component with inertia |

|

|---|---|---|

| speed |

Type: SpeedSensor Description: Ideal sensor to measure the absolute flange angular velocity |

|

| PI |

Type: PI Description: Discrete-time PI controller with clocked input and output signals (for periodic and aperiodic systems using the parameterization of the continuous PI controller) |

|

| feedback2 |

Type: Feedback Description: Output difference between commanded and feedback input |

|

| torque |

Type: Torque Description: Input signal acting as external torque on a flange |

|

| angle |

Type: AngleSensor Description: Ideal sensor to measure the absolute flange angle |

|

| kinematicPTP |

Type: KinematicPTP2 Description: Move as fast as possible from start to end position within given kinematic constraints with output signals q, qd=der(q), qdd=der(qd) |

|

| feedback1 |

Type: Feedback Description: Output difference between commanded and feedback input |

|

| gain |

Type: Gain Description: Output the product of a gain value with the input signal |

|

| sample1 |

Type: SampleClocked Description: Sample the continuous-time, Real input signal and provide it as clocked output signal. The clock is provided as input signal |

|

| sample2 |

Type: Sample Description: Sample the continuous-time, Real input signal and provide it as clocked output signal (clock is inferred) |

|

| hold1 |

Type: Hold Description: Hold the clocked, Real input signal and provide it as continuous-time output signal (zero order hold) |

|

| sample3 |

Type: SampleClocked Description: Sample the continuous-time, Real input signal and provide it as clocked output signal. The clock is provided as input signal |

|

| super |

Type: SuperSample Description: Super-sample the clocked Real input signal and provide it as clocked output signal |

|

| subSample1 |

Type: SubSample Description: Sub-sample the input clock and provide it as output clock |

|

| periodicRealClock |

Type: PeriodicRealClock Description: Generate a periodic clock signal with a period defined by a Real number |