WOLFRAM SYSTEM MODELER

FullAdderFull 1 Bit Adder Example |

|

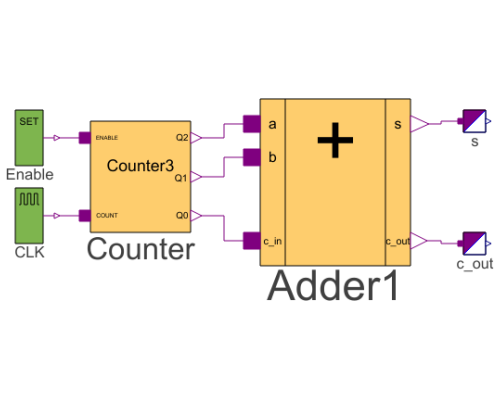

Diagram

Wolfram Language

SystemModel["Modelica.Electrical.Digital.Examples.FullAdder"]

Information

This information is part of the Modelica Standard Library maintained by the Modelica Association.

It is an adding circuit for binary numbers with input carry bit, which consists of two HalfAdders.

a.y, b.y and c.y are the inputs of the FullAdder.

cout = Or1.y and h.s are the outputs of the FullAdder.

t is the pick-up instant of the next bit(s) in the simulation.

a.y b.y c.y cout h.s t 1 0 0 0 1 1 0 1 0 0 1 2 0 0 1 0 1 3 1 1 0 1 0 4 0 1 1 1 0 5 1 0 1 1 0 6 1 1 1 1 1 7 0 0 0 0 0 8

The simulation stop time should be 10 seconds.

Components (6)

| Adder1 |

Type: FullAdder Description: Adding circuit for binary numbers with input carry bit |

|

|---|---|---|

| s |

Type: LogicToReal Description: Logic to Real converter |

|

| c_out |

Type: LogicToReal Description: Logic to Real converter |

|

| Counter |

Type: Counter3 Description: 3 Bit Counter |

|

| Enable |

Type: Set Description: Digital Set Source |

|

| CLK |

Type: DigitalClock Description: Digital Clock Source |