WOLFRAM SYSTEM MODELER

TestRealSampler |

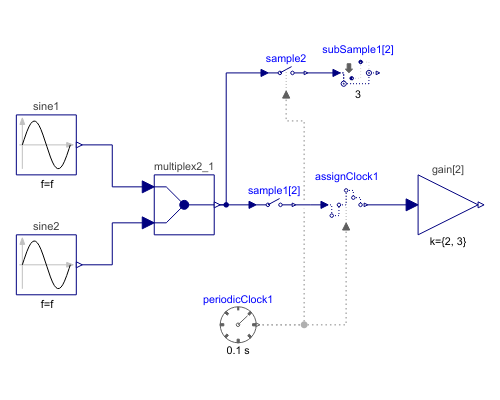

Diagram

Wolfram Language

SystemModel["Modelica_Synchronous.WorkInProgress.Tests.TestRealSampler"]

Components (9)

| sine1 |

Type: Sine Description: Generate sine signal |

|

|---|---|---|

| sine2 |

Type: Sine Description: Generate sine signal |

|

| multiplex2_1 |

Type: Multiplex2 Description: Multiplexer block for two input connectors |

|

| periodicClock1 |

Type: PeriodicRealClock Description: Generates a periodic clock signal with a period defined by a Real number |

|

| assignClock1 |

Type: AssignClockVectorized Description: Assigns a clock to a clocked Real signal vector |

|

| gain |

Type: Gain[2] Description: Output the product of a gain value with the input signal |

|

| sample1 |

Type: Sample[2] Description: Sample the continuous-time, Real input signal and provide it as clocked output signal (clock is inferred) |

|

| sample2 |

Type: SampleVectorizedAndClocked Description: Sample the continuous-time, Real input signal vector and provide it as clocked output signal vector. The clock is provided as input signal |

|

| subSample1 |

Type: SubSample[2] Description: Sub-sample the clocked Real input signal and provide it as clocked output signal |