WOLFRAM SYSTEM MODELER

LogicalSampleSimple example of conjunctive and disjunctive logical clocks, combining clock signals to derive new event driven clocks. |

|

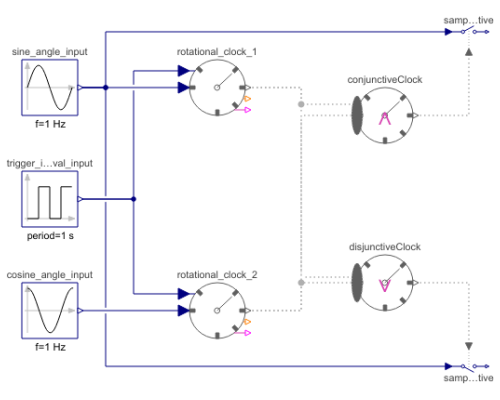

Diagram

Wolfram Language

SystemModel["Modelica.Clocked.Examples.Elementary.ClockSignals.LogicalSample"]

Information

This information is part of the Modelica Standard Library maintained by the Modelica Association.

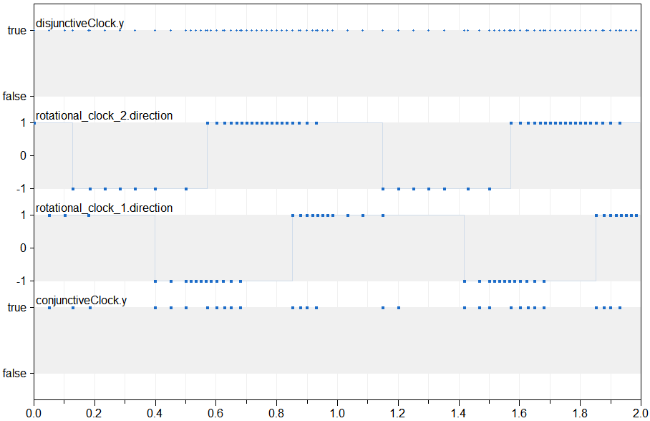

Simple example of two logical clocks, a conjunctive and a disjunctive clock. Both receive the very same clock inputs, produced by two rotational clocks with slightly shifted input angle waves (sine and cosine respectively). The configuration and results of the rotational clocks are explained in the rotational clocks example. The generated clocked signals of the disjunctive and conjunctive clock are therefore:

Components (9)

| sine_angle_input |

Type: Sine Description: Generate sine signal |

|

|---|---|---|

| cosine_angle_input |

Type: Cosine Description: Generate cosine signal |

|

| trigger_interval_input |

Type: Pulse Description: Generate pulse signal of type Real |

|

| rotational_clock_1 |

Type: RotationalClock Description: Event clock generating a clock tick each time an observed input angle changed for a rotational-interval given as variable input |

|

| rotational_clock_2 |

Type: RotationalClock Description: Event clock generating a clock tick each time an observed input angle changed for a rotational-interval given as variable input |

|

| conjunctiveClock |

Type: ConjunctiveClock Description: Logical clock ticking whenever all input clocks ticked at least once, then resets and starts the next conjunctive cycle |

|

| disjunctiveClock |

Type: DisjunctiveClock Description: Logical clock ticking whenever any of its input clock signals ticks. |

|

| sample_conjunctive |

Type: SampleClocked Description: Sample the continuous-time, Real input signal and provide it as clocked output signal. The clock is provided as input signal |

|

| sample_disjunctive |

Type: SampleClocked Description: Sample the continuous-time, Real input signal and provide it as clocked output signal. The clock is provided as input signal |