WOLFRAM SYSTEM MODELER

DFFREGPulse triggered D-Register-Bank, high active reset |

|

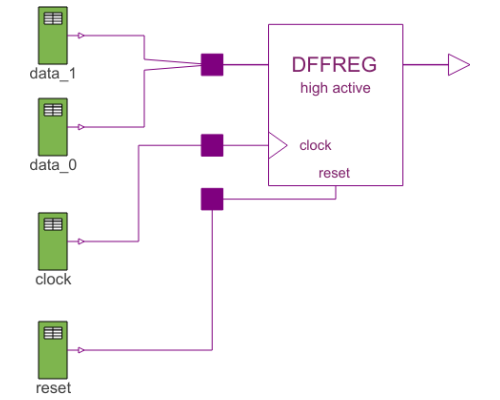

Diagram

Wolfram Language

In[1]:=

SystemModel["Modelica.Electrical.Digital.Examples.DFFREG"]

Out[1]:=

Information

This information is part of the Modelica Standard Library maintained by the Modelica Association.

This example is a simple test of the Registers.DFFREG component. The data width is set to two. After simulation plot both the dataIn and the dataOut vectors. To verify the results compare the truth table which is documented in the DFFREG component.

Components (5)

| clock |

Type: Table Description: Digital Tabular Source |

|

|---|---|---|

| data_0 |

Type: Table Description: Digital Tabular Source |

|

| reset |

Type: Table Description: Digital Tabular Source |

|

| data_1 |

Type: Table Description: Digital Tabular Source |

|

| dFFREG |

Type: DFFREG Description: Edge triggered register bank with high active reset |