WOLFRAM SYSTEM MODELER

AssignClockVectorizedExample of a AssignClockVectorized block for Real signals |

|

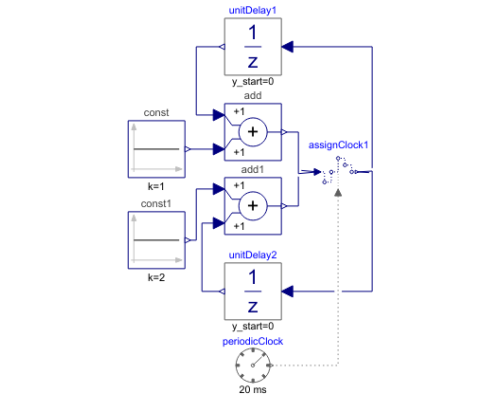

Diagram

Wolfram Language

SystemModel["Modelica_Synchronous.Examples.Elementary.RealSignals.AssignClockVectorized"]

Information

Example used to generate a figure for the documentation of block Modelica_Synchronous.RealSignals.Sampler.AssignClockVectorized.

Components (8)

| periodicClock |

Type: PeriodicExactClock Description: Generates a periodic clock signal with a period defined by an Integer number with resolution |

|

|---|---|---|

| unitDelay1 |

Type: UnitDelay Description: Delays the clocked input signal for one sample period |

|

| add |

Type: Add Description: Output the sum of the two inputs |

|

| const |

Type: Constant Description: Generate constant signal of type Real |

|

| assignClock1 |

Type: AssignClockVectorized Description: Assigns a clock to a clocked Real signal vector |

|

| add1 |

Type: Add Description: Output the sum of the two inputs |

|

| const1 |

Type: Constant Description: Generate constant signal of type Real |

|

| unitDelay2 |

Type: UnitDelay Description: Delays the clocked input signal for one sample period |