WOLFRAM SYSTEM MODELER

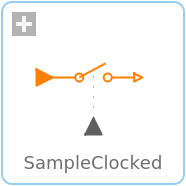

SampleClockedSample the continuous-time, Integer input signal and provide it as clocked output signal. The clock is provided as input signal |

|

Wolfram Language

SystemModel["Modelica_Synchronous.IntegerSignals.Sampler.SampleClocked"]

Information

This block for Integer signals works similarly as the corresponding block for Real signals (see RealSignals.Sampler.SampleClocked).

Analog to the corresponding Real signal block example there exists an elementary example for this Integer block.

Connectors (3)

| clock |

Type: ClockInput Description: Output signal y is associated with this clock input |

|

|---|---|---|

| u |

Type: IntegerInput Description: Connector of continuous-time, Integer input signal |

|

| y |

Type: IntegerOutput Description: Connector of clocked, Integer output signal |

Used in Examples (10)

|

Modelica_Synchronous.Examples.Elementary.IntegerSignals Example of a Sample block for Integer signals with direct feed-through in the continuous-time and the clocked partition |

|

|

Modelica_Synchronous.Examples.Elementary.IntegerSignals Example of a SampleClocked block for Integer signals |

|

|

Modelica_Synchronous.Examples.Elementary.IntegerSignals Example of a Hold block for Integer signals |

|

|

Modelica_Synchronous.Examples.Elementary.IntegerSignals Example of a SubSample block for Integer signals |

|

|

Modelica_Synchronous.Examples.Elementary.IntegerSignals Example of a SuperSample block for Integer signals |

|

|

Modelica_Synchronous.Examples.Elementary.IntegerSignals Example of a ShiftSample block for Integer signals |

|

|

Modelica_Synchronous.Examples.Elementary.IntegerSignals Example of a BackSample block for Integer signals |

|

|

Modelica_Synchronous.Examples.Elementary.IntegerSignals Example of an UpSample block for Integer signals |

|

|

Modelica_Synchronous.WorkInProgress.Tests |

|

|

Modelica_Synchronous.WorkInProgress.Tests |