WOLFRAM SYSTEM MODELER

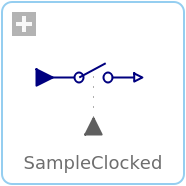

SampleClockedSample the continuous-time, Real input signal and provide it as clocked output signal. The clock is provided as input signal |

|

Wolfram Language

SystemModel["Modelica_Synchronous.RealSignals.Sampler.SampleClocked"]

Information

Note, it does not make much sense to vectorize this block, because then also the clock input is vectorized. Instead, if the input signal is a vector, use block SampleVectorizedAndClocked that has a vector Real input and output, as well as a scalar clock input.

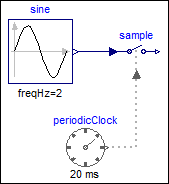

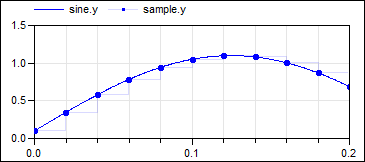

Example

The following

example

samples a sine signal with a periodic clock of 20 ms period:

|

|

|

| model | simulation result |

Connectors (3)

| u |

Type: RealInput Description: Connector of continuous-time, Real input signal |

|

|---|---|---|

| y |

Type: RealOutput Description: Connector of clocked, Real output signal |

|

| clock |

Type: ClockInput Description: Output signal y is associated with this clock input |

Used in Examples (46)

|

ClockedWithDiscreteTextbookController Modelica_Synchronous.Examples.SimpleControlledDrive Simple controlled drive with discrete textbook controller (period is not used in the controller) |

|

|

Modelica_Synchronous.Examples.SimpleControlledDrive Simple controlled drive with discrete controller (period is used in the controller) |

|

|

ExactlyClockedWithDiscreteController Modelica_Synchronous.Examples.SimpleControlledDrive Simple controlled drive with discrete controller and exact periodic clocks (period is used in the controller) |

|

|

ClockedWithDiscretizedContinuousController Modelica_Synchronous.Examples.SimpleControlledDrive Simple controlled drive with discretized continuous-time controller |

|

|

Modelica_Synchronous.Examples.CascadeControlledDrive Drive with clocked cascade controller where clocks are defined with sub-sampling and partitions with super-sampling |

|

|

Modelica_Synchronous.Examples.CascadeControlledDrive Drive with clocked cascade controller where fastest partition is defined with a clock and slower partition is defined with super-sampling |

|

|

Modelica_Synchronous.Examples.CascadeControlledDrive Drive with clocked cascade controller where all partitions are defined with exact (integer) clock that need to be compatible to each other |

|

|

Modelica_Synchronous.Examples.Systems Simple example of a mixing unit where a (discretized) nonlinear inverse plant model is used as feedforward controller |

|

|

Modelica_Synchronous.Examples.Systems |

|

|

Modelica_Synchronous.Examples.Elementary.ClockSignals Example of a SubSample block for Clock signals |

|

|

Modelica_Synchronous.Examples.Elementary.ClockSignals Example of a SuperSample block for Clock signals |

|

|

Modelica_Synchronous.Examples.Elementary.ClockSignals Example of a ShiftSample block for Clock signals |

|

|

Modelica_Synchronous.Examples.Elementary.ClockSignals Simple example of a rotational clock with variable trigger interval and switching rotation-direction. |

|

|

Modelica_Synchronous.Examples.Elementary.RealSignals Example of a Sample block for Real signals with direct feed-through in the continuous-time and the clocked partition |

|

|

Modelica_Synchronous.Examples.Elementary.RealSignals Example of a SampleClocked block for Real signals |

|

|

Modelica_Synchronous.Examples.Elementary.RealSignals Example of a Hold block for Real signals |

|

|

Modelica_Synchronous.Examples.Elementary.RealSignals Example of a HoldWithDAeffects block for Real signals |

|

|

Modelica_Synchronous.Examples.Elementary.RealSignals Example of a HoldWithDAeffects block for Real signals (with a computational delay of one sample period) |

|

|

Modelica_Synchronous.Examples.Elementary.RealSignals Example of a SubSample block for Real signals |

|

|

Modelica_Synchronous.Examples.Elementary.RealSignals Example of a SuperSample block for Real signals |

|

|

Modelica_Synchronous.Examples.Elementary.RealSignals Example of a SuperSampleInterpolated block for Real signals |

|

|

Modelica_Synchronous.Examples.Elementary.RealSignals Example of a ShiftSample block for Real signals |

|

|

Modelica_Synchronous.Examples.Elementary.RealSignals Example of a BackSample block for Real signals |

|

|

Modelica_Synchronous.Examples.Elementary.RealSignals Example of an UpSample block for Real signals |

|

|

Modelica_Synchronous.Examples.Elementary.RealSignals Example of an UpSample block for Real signals combined with FIR filter blocks |

|

|

Modelica_Synchronous.Examples.Elementary.RealSignals Example of an AssignClockToTriggerHold block for Real signals |

|

|

Modelica_Synchronous.Examples.Elementary.RealSignals Example of an AssignClockToSquareWaveHold block for Real signals |

|

|

Modelica_Synchronous.Examples.Elementary.RealSignals Example of a UniformNoise block for Real signals |

|

|

Modelica_Synchronous.Examples.Elementary.RealSignals Example of a FractionalDelay block for Real signals |

|

|

Modelica_Synchronous.WorkInProgress.Tests |

|

|

Modelica_Synchronous.WorkInProgress.Tests |

|

|

Modelica_Synchronous.WorkInProgress.Tests |

|

|

Modelica_Synchronous.WorkInProgress.Tests |

|

|

Modelica_Synchronous.WorkInProgress.Tests |

|

|

Modelica_Synchronous.WorkInProgress.Tests |

|

|

Modelica_Synchronous.WorkInProgress.Tests |

|

|

Modelica_Synchronous.WorkInProgress.Tests |

|

|

Modelica_Synchronous.WorkInProgress.Tests |

|

|

Modelica_Synchronous.WorkInProgress.Tests |

|

|

Modelica_Synchronous.WorkInProgress.Tests |

|

|

Modelica_Synchronous.WorkInProgress.Tests |

|

|

Modelica_Synchronous.WorkInProgress.Tests |

|

|

Modelica_Synchronous.WorkInProgress.Tests |

|

|

Modelica_Synchronous.WorkInProgress.Tests |

|

|

Modelica_Synchronous.WorkInProgress.Tests |

|

|

Modelica_Synchronous.WorkInProgress.Tests.Effects Different ways to super sample a signal |

Used in Components (2)

|

Modelica_Synchronous.ClockSignals.Clocks.Rotational Event clock generating a clock tick each time an observed input angle changed for a rotational-interval given as variable input. |

|

|

Modelica_Synchronous.WorkInProgress.Incubate |