WOLFRAM SYSTEM MODELER

TestIntegerSamplerAndHolds |

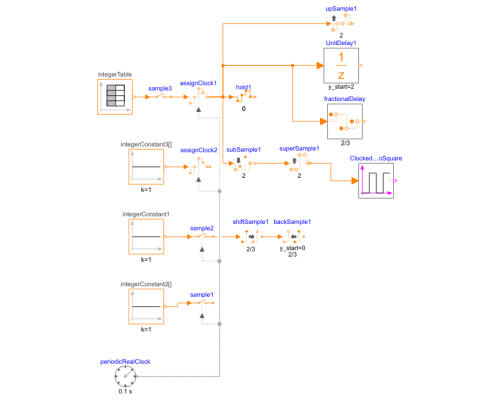

Diagram

Wolfram Language

SystemModel["Modelica_Synchronous.WorkInProgress.Tests.TestIntegerSamplerAndHolds"]

Components (19)

| assignClock1 |

Type: AssignClock Description: Assigns a clock to a clocked Integer signal |

|

|---|---|---|

| periodicRealClock |

Type: PeriodicRealClock Description: Generates a periodic clock signal with a period defined by a Real number |

|

| hold1 |

Type: Hold Description: Hold the clocked, Integer input signal and provide it as continuous-time output signal (zero order hold) |

|

| integerConstant1 |

Type: IntegerConstant Description: Generate constant signal of type Integer |

|

| sample2 |

Type: SampleClocked Description: Sample the continuous-time, Integer input signal and provide it as clocked output signal. The clock is provided as input signal |

|

| sample1 |

Type: SampleVectorizedAndClocked Description: Sample the continuous-time, Integer input signal vector and provide it as clocked output signal vector. The clock is provided as input signal |

|

| integerConstant2 |

Type: IntegerConstant[3] Description: Generate constant signal of type Integer |

|

| integerConstant3 |

Type: IntegerConstant[3] Description: Generate constant signal of type Integer |

|

| assignClock2 |

Type: AssignClockVectorized Description: Assigns a clock to a clocked Integer signal vector |

|

| subSample1 |

Type: SubSample Description: Sub-sample the clocked Integer input signal and provide it as clocked output signal |

|

| superSample1 |

Type: SuperSample Description: Super-sample the clocked Integer input signal and provide it as clocked output signal |

|

| shiftSample1 |

Type: ShiftSample Description: Shift the clocked Integer input signal by a fraction of the last interval and and provide it as clocked output signal |

|

| backSample1 |

Type: BackSample Description: Shift clock of Integer input signal backwards in time (and access the most recent value of the input at this new clock) |

|

| integerTable |

Type: IntegerTable Description: Generate an Integer output signal based on a table matrix with [time, yi] values |

|

| sample3 |

Type: Sample Description: Sample the continuous-time, Integer input signal and provide it as clocked output signal (clock is inferred) |

|

| upSample1 |

Type: UpSample Description: Upsample the clocked Integer input signal and provide it as clocked output signal |

|

| UnitDelay1 |

Type: UnitDelay Description: Delays the clocked input signal for one sample period |

|

| fractionalDelay |

Type: FractionalDelay Description: Delays the clocked input signal for a fractional multiple of the sample period |

|

| ClockedSignalToSquare |

Type: AssignClockToSquareWaveHold Description: Generate a Boolean continuous-time square signal from a clocked Integer input |