WOLFRAM SYSTEM MODELER

HoldWithDAeffectsHold with (simulated) Digital-Analog converter effects and computational delay |

|

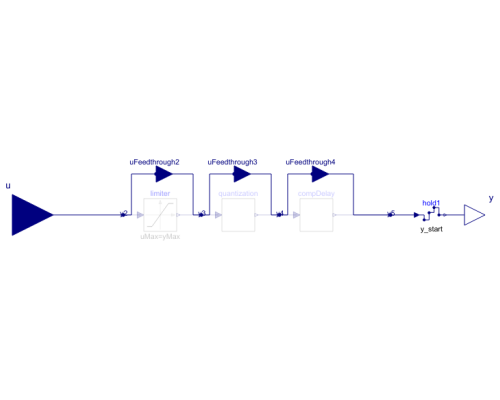

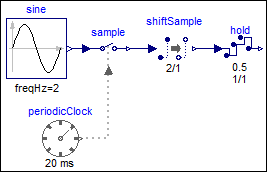

Diagram

Wolfram Language

SystemModel["Modelica_Synchronous.RealSignals.Sampler.HoldWithDAeffects"]

Information

- The output is delayed by a fraction of the clock period, if parameter computationalDelay = true. The delay is defined by shiftCounter/resolution*interval(), where shiftCounter and resolution are Integer parameters and interval() is the time duration from the previous to the current clock tick. The maximal possible computational delay is one clock duration, and therefore there is the restriction that shiftCounter ≤ resolution.

- The output is limited, if parameter limited = true.

- The output is value discretized in the form of an Digital-Analog converter with a defineable number of bits, if parameters limited = true, and quantized = true.

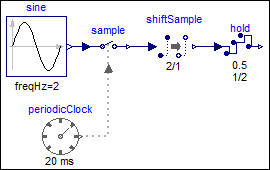

Example

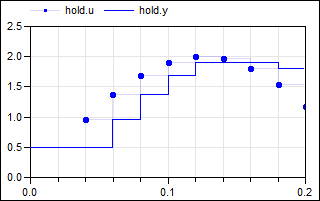

The following example samples a sine signal with an amplitude of 2.0 with a periodic clock of 20 ms period and delays it for 2 sample periods. The resulting signal is hold with the HoldWithDAeffects block. As a result, the clock of hold.u starts ticking at 40 ms. The output hold.y of the block is a continuous-time signal that is present from the start of the simulation. Before the first tick of the clock of hold.u, it is set to 0.5 (= the value of parameter hold.y_start). Additionally, the following effects are added to the hold block:

- The output is limited to +/- 1.9.

- A computational delay of half of a sample period (= 1/2*20 ms = 10 ms)

is defined.

|

|

|

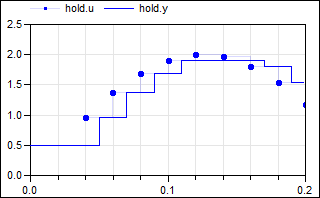

| model | simulation result |

Due to the limitation of the output signal, the values of hold.u ≥ 1.9

are limited to 1.9.

If the hold output is delayed by one sample period, then the previous(..) value of the

input is output, and the first tick is delayed by one sample period,

as shown by the

modified example

from above:

|

|

|

| model | simulation result |

Note, the computational delay of one sample period is defined

by shiftCounter=1, resolution=1, as shown in the icon of the

hold block.

Parameters (9)

| y_start |

Value: 0.0 Type: Real Description: Value of output y before the first tick of the clock associated to input u |

|---|---|

| computationalDelay |

Value: false Type: Boolean Description: =true, if a computational delay should be imposed |

| shiftCounter |

Value: 0 Type: Integer Description: (min=0, max=resolution), computational delay = interval()*shiftCounter/resolution |

| resolution |

Value: 1 Type: Integer Description: Time quantization resolution of sample interval |

| limited |

Value: false Type: Boolean Description: = true, if output is limited |

| quantized |

Value: false Type: Boolean Description: = true, if output quantization effects included |

| yMax |

Value: 1 Type: Real Description: Upper limit of output (if limited = true) |

| yMin |

Value: -yMax Type: Real Description: Lower limit of output (if limited = true) |

| bits |

Value: 8 Type: Integer Description: Number of bits of quantization (if quantized = true) |

Connectors (9)

| u |

Type: RealInput Description: Connector of clocked, Real input signal |

|

|---|---|---|

| y |

Type: RealOutput Description: Connector of continuous-time, Real output signal |

|

| uFeedthrough2 |

Type: RealInput Description: 'input Real' as connector |

|

| uFeedthrough3 |

Type: RealInput Description: 'input Real' as connector |

|

| uFeedthrough4 |

Type: RealInput Description: 'input Real' as connector |

|

| y2 |

Type: RealOutput Description: 'output Real' as connector |

|

| y3 |

Type: RealOutput Description: 'output Real' as connector |

|

| y4 |

Type: RealOutput Description: 'output Real' as connector |

|

| y5 |

Type: RealOutput Description: 'output Real' as connector |

Components (4)

| limiter |

Type: Limiter Description: Limit the range of a signal |

|

|---|---|---|

| quantization |

Type: Quantization Description: DAC quantization effects |

|

| compDelay |

Type: ComputationalDelay Description: Delays a clocked signal for at most one period, in order to model a computational delay |

|

| hold1 |

Type: Hold Description: Hold the clocked, Real input signal and provide it as continuous-time output signal (zero order hold) |

Used in Examples (5)

|

Modelica_Synchronous.Examples.SimpleControlledDrive Simple controlled drive with discrete controller and simulated AD and DA effects |

|

|

Modelica_Synchronous.Examples.Elementary.RealSignals Example of a HoldWithDAeffects block for Real signals |

|

|

Modelica_Synchronous.Examples.Elementary.RealSignals Example of a HoldWithDAeffects block for Real signals (with a computational delay of one sample period) |

|

|

Modelica_Synchronous.WorkInProgress.Tests Using partial sample and hold blocks to allow redeclaration of blocks to simulated communication blocks |

|

|

Modelica_Synchronous.WorkInProgress.Tests |