WOLFRAM SYSTEM MODELER

JKFFJK FlipFlop |

|

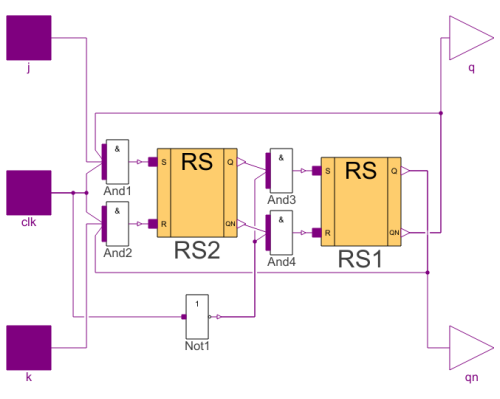

Diagram

Wolfram Language

SystemModel["Modelica.Electrical.Digital.Examples.Utilities.JKFF"]

Information

This information is part of the Modelica Standard Library maintained by the Modelica Association.

Basing on the RS component JKFF is a J-K-flipflop composed according the schematic. Its parameter delayTime is the delay time of the RS component transport delay, q0 is the initial value of that delay.

Parameters (2)

Connectors (5)

| j |

Type: DigitalInput Description: Input DigitalSignal as connector |

|

|---|---|---|

| q |

Type: DigitalOutput Description: Output DigitalSignal as connector |

|

| qn |

Type: DigitalOutput Description: not Q |

|

| clk |

Type: DigitalInput Description: Input DigitalSignal as connector |

|

| k |

Type: DigitalInput Description: Input DigitalSignal as connector |

Components (7)

| RS1 |

Type: RS Description: Unclocked RS FlipFlop |

|

|---|---|---|

| RS2 |

Type: RS Description: Unclocked RS FlipFlop |

|

| And1 |

Type: And Description: And logic component with multiple input and one output |

|

| And2 |

Type: And Description: And logic component with multiple input and one output |

|

| And3 |

Type: And Description: And logic component with multiple input and one output |

|

| And4 |

Type: And Description: And logic component with multiple input and one output |

|

| Not1 |

Type: Not Description: Not logic component without delay |

Used in Examples (2)

|

Modelica.Electrical.Digital.Examples 4 to 1 Bit Multiplexer Example |

|

|

Modelica.Electrical.Digital.Examples Pulse Triggered Master Slave Flip-Flop |